インテル、HPC向けに新しい“MIC”アーキテクチャCPUの投入を発表 ~ 22nm技術を採用

エンタープライズ

ハードウェア

注目記事

-

10G光回線導入レポ

-

【COMPUTEX TAIPEI 2010(Vol.2)】インテル、モバイル向けデュアルコアAtom搭載の超薄型ネットブックを披露

-

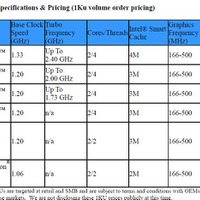

インテル、薄型・軽量ノート向けの超低電圧版Core iシリーズを発表

ドイツのハンブルグで開催中の「International Supercomputing Conference」(ISC)において発表された。第一弾としては、調査・科学研究・金融・気候シミュレーションなどのハイパフォーマンスコンピューティング(HPC)分野向けに、「Knights Corner」(開発コード名)をインテルの22ナノメートル(nm)プロセス技術により製造する予定となっている。

「Knights Corner」は、1メートルの10億分の22メートルの大きさのトランジスターを集積し、ムーアの法則に基づき単一のチップ上に50以上のインテル・プロセッサー・コアを搭載するという。業界向け設計および開発キットの「Knights Ferry」(開発コード名)は現在、一部の開発者向けに出荷されており、インテルは、2010年後半から“インテルMICアーキテクチャー”向けの広範な開発者向けツールを提供するプログラムを拡大する予定。なお“インテルMICアーキテクチャー”は「Larrabee」(開発コード名)を含むインテルの複数のプロジェクトや、シングルチップ・クラウド・コンピュータなどインテル・ラボの研究プロジェクトから誕生したものとのこと。

欧州原子核研究機構(CERN)オープンラボCTO(最高技術責任者)のスヴェール・ジャープ氏は「CERNオープンラボのチームはわずか数日で、複雑なC++並列ベンチマークをインテルMICソフトウェア開発プラットフォームに移行できました。精通したハードウェア・プログラミング・モデルにより、われわれはソフトウェアを予想以上の速度で実行することが可能になりました」とのコメントを寄せている。

なお「International Supercomputing Conference」(ISC)で発表された第35回の「TOP500」 リストでは、およそ82%の408システムがインテル・プロセッサーを採用しており、引き続きハイパフォーマンス・コンピューティング分野での勢力を持続しており、90%以上のクアッドコア・プロセッサー・ベースのシステムがインテル・プロセッサーを採用しているとのこと。インテルXeonプロセッサー5500番台は前回のリストの95システムから186システムに採用数が増加した。

《冨岡晶》

特集

この記事の写真

/