東芝、立体構造トランジスタでオン電流を従来比58%向上させる歪み印加技術を実証

エンタープライズ

ハードウェア

注目記事

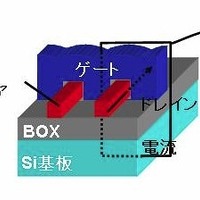

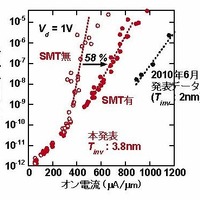

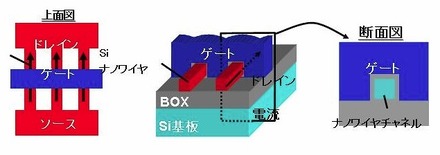

「ナノワイヤトランジスタ」は、トランジスタ構造の有力候補として検討されている立体構造トランジスタで、トランジスタのチャンネル部がナノメートル級の細いワイヤ形状のシリコンから生成されている。細線状のチャンネルをゲートが取り囲む構造のため、ゲートによる制御性能が向上しており、短チャンネル効果によるオフ時リーク電流の大幅な抑制が可能となっている。通常のナノワイヤトランジスタはオン電流が低いため、同社ではオン電流を向上させるための技術を開発しており、今年6月に、ゲート側壁加工の最適化と結晶方位の回転によりオン電流を向上する技術を開発していた。

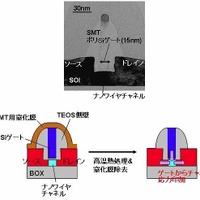

今回作製されたトランジスタは、トランジスタにおける性能向上技術である応力印加手法の1つである「ストレスメモライゼーション技術」(SMT)をナノワイヤトランジスタに適用したもの。SMTでは、ゲート電極からチャンネルに応力を印加することにより、ナノワイヤチャンネルの結晶を歪ませ、チャンネル中のキャリア移動度が向上するという。今回作製されたトランジスタでは、n型トランジスタのオン電流が、オフ電流100nA/mmのもとで従来比58%向上した。今回の実験により、ナノワイヤ構造にした方がSMTの効果が増すことが確認され、ゲート電極からの応力印加がナノワイヤトランジスタにおいて有効であることが実証されたとのこと。

今後東芝は、今年6月に開発したゲート側壁加工技術と今回のストレスメモライゼーション技術を、より絶縁膜を薄くしたトランジスタに適用することにより、従来比で2倍以上のオン電流を実現するトランジスタの開発を目指す。なおこの成果は、12月6日から米国・サンフランシスコで開催される半導体デバイスに関する国際学会「IEDM 2010」で、8日(現地時間)に発表される予定。

《冨岡晶》

特集

この記事の写真

/