富士通、CPU間のデータ通信を約2倍に高速化する送受信回路を開発……スパコン高性能化に期待

エンタープライズ

ハードウェア

注目記事

-

10G光回線導入レポ

-

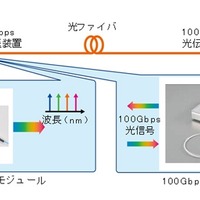

三菱電機、「100Gbps光伝送」を構成する各種技術を開発……都市間通信を高速大容量化

-

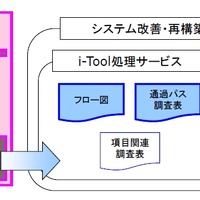

アイ・システムのプログラム解析・可視化ツール「i-Tool」、VB6.0、C#、VBAに対応

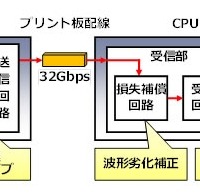

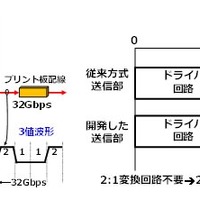

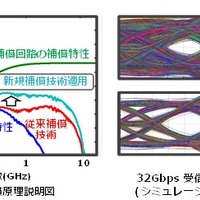

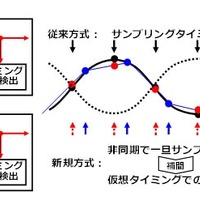

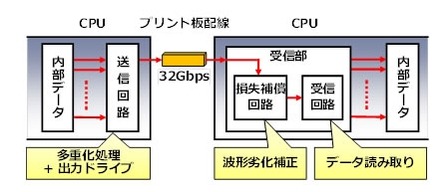

送信回路、受信部の損失補償回路、および受信回路に新方式の回路技術を採用することにより高速化を実現した。送信回路では多チャンネルのデータを1チャンネルに多重化して送信するが、最終段の多重化回路(2:1変換回路)を不要とする送信回路を開発した。受信部の損失補償回路では、低域側の周波数特性をフラット化し、信号損失を補償する回路を開発。従来32Gbpsでは実現できなかった80センチメートル(cm)の伝送距離でもデータの読み取りが可能な信号波形を得ることに成功した。受信回路では、仮想信号を合成するデータ補間方式(データインターポレーション方式)を開発し、高精度な時間軸方向の分解能が要求されるタイミング調整回路を不要とした。

現在のサーバは、数Gbps~十数Gbpsのデータ通信速度で活用されているが、新回路は従来の約2倍の高速化を実現しており、次世代サーバやスーパーコンピュータなどの性能向上に貢献することが期待される。

同社では今後、今回開発した技術を、サーバを構成するボード間のバックプレーンインターフェイスなど、ビックデータを扱う製品分野への適用を進めていく計画だ。

《冨岡晶》

特集

この記事の写真

/